——Podijeljeno od DWIN Frouma

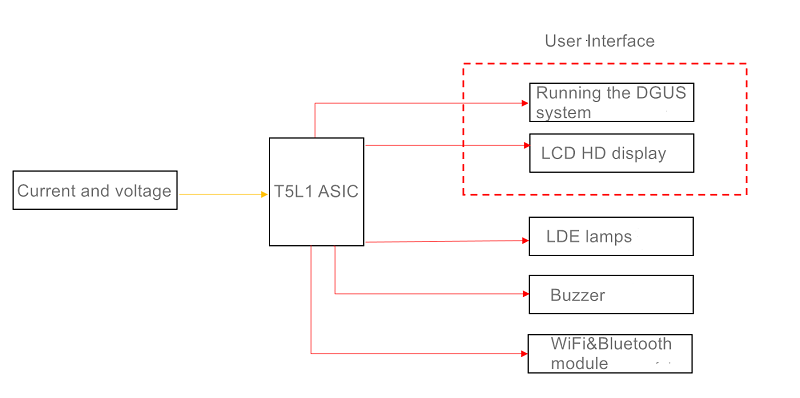

Koristeći DWIN T5L1 čip kao kontrolno jezgro cijele mašine, prima i obrađuje dodir, ADC akviziciju, PWM upravljačke informacije i pokreće 3,5-inčni LCD ekran za prikaz trenutnog statusa u realnom vremenu.Podržava daljinsko podešavanje svjetline LED izvora svjetlosti putem WiFi modula i podržava glasovni alarm.

Karakteristike programa:

1. Usvojite T5L čip za rad na visokoj frekvenciji, AD analogno uzorkovanje je stabilno, a greška je mala;

2. Podržava TIP C direktno povezan na PC za otklanjanje grešaka i snimanje programa;

3. Podržava brzi OS jezgro interfejs, 16-bitni paralelni port;UI core PWM port, izlaz AD porta, jeftin dizajn aplikacije, nema potrebe za dodavanjem dodatnog MCU-a;

4. Podrška WiFi, Bluetooth daljinski upravljač;

5. Podržava 5~12V DC široki napon i široki opseg ulaza

1.1 Shema dijagrama

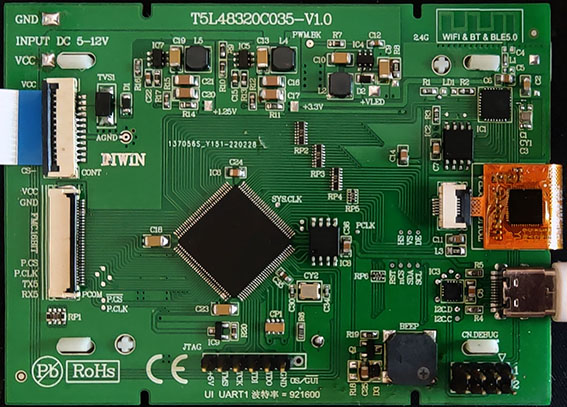

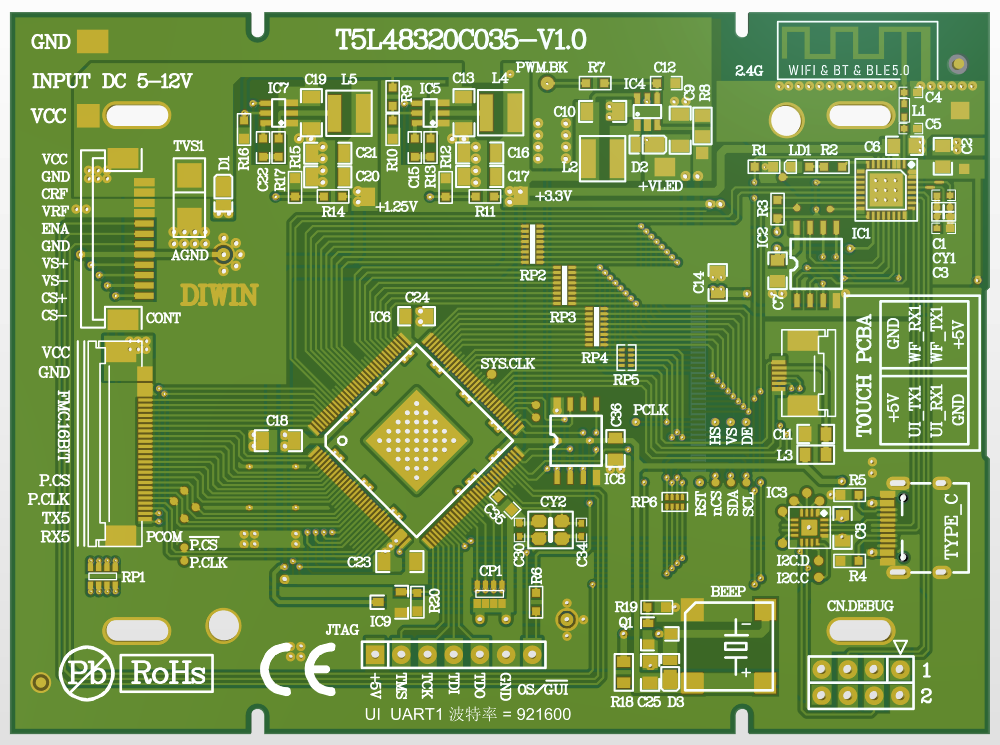

1.2 PCB ploča

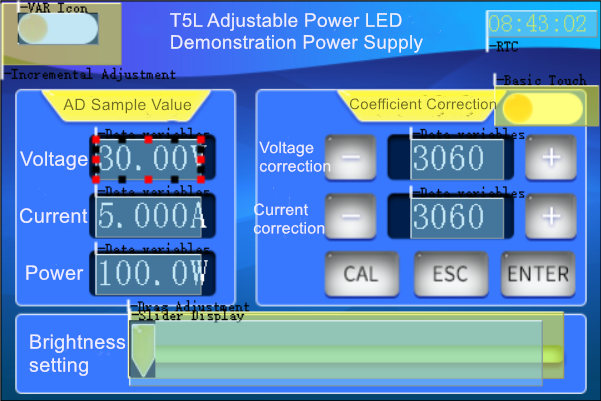

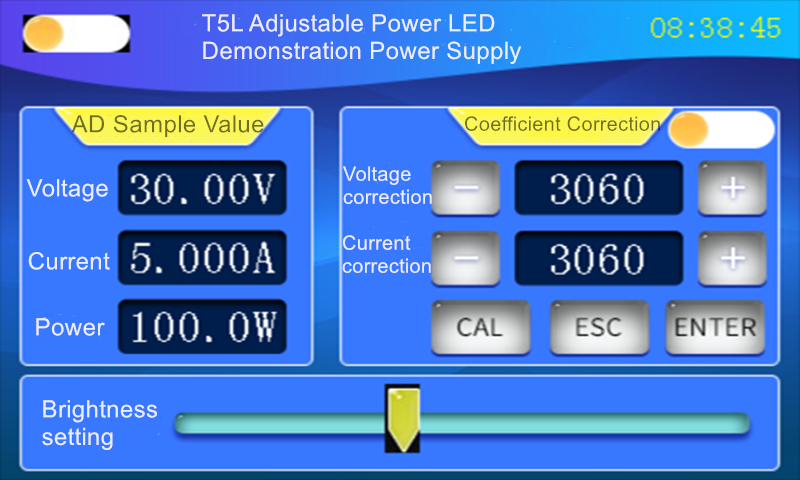

1.3 Korisničko sučelje

Sramota uvod:

(1) Dizajn hardverskog kola

1.4 Šema strujnog kruga T5L48320C035

1. MCU logičko napajanje 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU jezgro napajanja 1.25V: C23, C24;

3. MCU analogno napajanje 3.3V: C35 je analogno napajanje za MCU.Prilikom slaganja, uzemljenje jezgra od 1,25 V i logičko uzemljenje mogu se kombinirati zajedno, ali analogno uzemljenje mora biti odvojeno.Analogno uzemljenje i digitalno uzemljenje treba da se sakupe na negativnom polu LDO izlaznog velikog kondenzatora, a analogni pozitivni pol takođe treba da se sakupe na pozitivnom polu LDO velikog kondenzatora, tako da se šum uzorkovanja AD minimizira.

4. AD kolo za akviziciju analognog signala: CP1 je AD analogni ulazni filter kondenzator.Kako bi se smanjila greška uzorkovanja, analogno i digitalno uzemljenje MCU-a su odvojene nezavisno.Negativni pol CP1 mora biti spojen na analognu masu MCU-a sa minimalnom impedansom, a dva paralelna kondenzatora kristalnog oscilatora su povezana na analognu masu MCU-a.

5. Kolo zujalice: C25 je kondenzator napajanja za zujalicu.Zujalica je induktivni uređaj i tokom rada će postojati vršna struja.Da bi se smanjio vrh, potrebno je smanjiti MOS pogonsku struju zujalice kako bi MOS cijev radila u linearnom području i dizajnirati kolo tako da radi u režimu prekidača.Imajte na umu da R18 treba biti spojen paralelno na oba kraja zujalice kako bi se podesio kvalitet zvuka zujalice i kako bi zvuk zujalice bio oštar i prijatan.

6. WiFi kolo: uzorkovanje WiFi čipa ESP32-C, sa WiFi+Bluetooth+BLE.Na ožičenju, uzemljenje RF napajanja i uzemljenje signala su odvojeni.

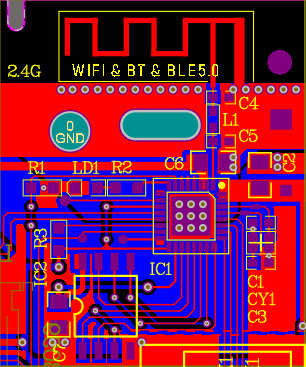

Dizajn 1.5 WiFi kola

Na gornjoj slici, gornji dio bakrenog premaza je petlja za uzemljenje.Petlja uzemljenja refleksije WiFi antene mora imati veliku površinu do uzemljenja napajanja, a tačka sakupljanja uzemljenja napajanja je negativni pol C6.Reflektovana struja mora biti osigurana između uzemljenja i WiFi antene, tako da ispod WiFi antene mora postojati bakarni premaz.Dužina bakrenog premaza premašuje dužinu proširenja WiFi antene, a produžetak će povećati osjetljivost WiFi;tačka na negativnom polu C2.Velika površina bakra može zaštititi šum uzrokovan zračenjem WiFi antene.2 bakrena uzemljenja se odvajaju na donjem sloju i skupljaju na srednji jastučić ESP32-C kroz otvore.RF uzemljenje za napajanje treba nižu impedanciju od petlje za uzemljenje signala, tako da postoji 6 prolaza od uzemljenja napajanja do čip jastučića kako bi se osigurala dovoljno niska impedansa.Petlja uzemljenja kristalnog oscilatora ne može imati RF snagu koja teče kroz nju, inače će kristalni oscilator generirati podrhtavanje frekvencije, a pomak WiFi frekvencije neće moći slati i primati podatke.

7. Krug napajanja LED pozadinskog osvjetljenja: uzorkovanje čipa upravljačkog programa SOT23-6LED.DC/DC napajanje za LED nezavisno formira petlju, a DC/DC uzemljenje je povezano sa 3.3V LOD uzemljenjem.Pošto je jezgro PWM2 porta specijalizovano, on emituje 600K PWM signal, a dodat je RC da koristi PWM izlaz kao ON/OFF kontrolu.

8. Opseg ulaznog napona: dizajnirana su dva DC/DC stupnja pada.Imajte na umu da otpornici R13 i R17 u DC/DC kolu ne mogu biti izostavljeni.Dva DC/DC čipa podržavaju ulaz do 18V, što je pogodno za vanjsko napajanje.

9. USB TYPE C port za otklanjanje grešaka: TIP C se može priključiti i isključiti naprijed i nazad.Umetanje unapred komunicira sa WIFI čipom ESP32-C za programiranje WIFI čipa;obrnuto umetanje komunicira sa XR21V1410IL16 za programiranje T5L.TIP C podržava napajanje od 5V.

10. Komunikacija sa paralelnim portom: jezgro T5L OS-a ima mnogo slobodnih IO portova, a može se dizajnirati komunikacija sa 16-bitnim paralelnim portom.U kombinaciji sa ST ARM FMC protokolom paralelnog porta, podržava sinhrono čitanje i pisanje.

11. LCM RGB dizajn interfejsa velike brzine: T5L RGB izlaz je direktno povezan sa LCM RGB, a otpor bafera je dodat u sredini kako bi se smanjile smetnje LCM talasanja vode.Prilikom ožičenja, smanjite dužinu veze RGB interfejsa, posebno PCLK signala, i povećajte testne tačke RGB interfejsa PCLK, HS, VS, DE;SPI port ekrana je povezan sa P2.4~P2.7 portovima T5L, što je pogodno za dizajniranje drajvera ekrana.Vodite RST, nCS, SDA, SCI testne tačke kako biste olakšali razvoj osnovnog softvera.

(2) DGUS interfejs

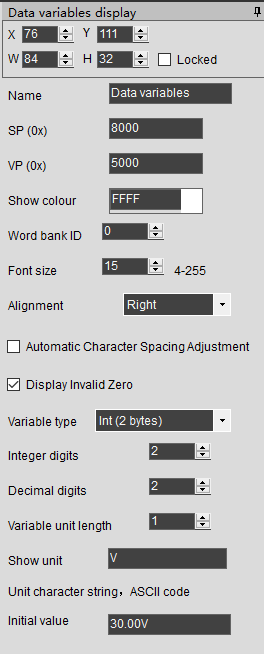

1.6 Kontrola prikaza varijabli podataka

(3) OS

//———————————DGUS format za čitanje i pisanje

typedef struct

{

u16 addr;//UI 16-bitna varijabla adresa

u8 datLen;//8bitdata length

u8 *pBuf;//8-bitni pokazivač podataka

} UI_packTypeDef;//DGUS čitanje i pisanje paketa

//————————————kontrola prikaza varijabli podataka

typedef struct

{

u16 VP;

u16 X;

u16 Y;

u16 Boja;

u8 Lib_ID;

u8 FontSize;

u8 Algnment;

u8 IntNum;

u8 DecNum;

u8 Type;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;// struktura opisa varijable podataka

typedef struct

{

Number_spTypeDef sp;//definiraj pokazivač opisa SP

UI_packTypeDef spPack;//definiraj SP varijablu DGUS paket za čitanje i pisanje

UI_packTypeDef vpPack;//definiraj vp varijablu DGUS paket za čitanje i pisanje

} Number_HandleTypeDef;//struktura varijable podataka

Sa prethodnom definicijom ručke varijable podataka.Zatim definirajte varijablu za prikaz uzorkovanja napona:

Number_HandleTypeDef Hsample;

u16 voltage_sample;

Prvo, izvršite funkciju inicijalizacije

BrojSP_Init(&Hsample,voltage_sample,0×8000);//0×8000 ovdje je pokazivač opisa

//——Varijabla podataka koja pokazuje inicijalizaciju strukture SP pokazivača——

void NumberSP_Init(Number_HandleTypeDef *broj,u8 *vrijednost, u16 brojAddr)

{

broj->spPack.addr = brojAddr;

broj->spPack.datLen = sizeof(broj->sp);

broj->spPack.pBuf = (u8 *)&broj->sp;

Read_Dgus(&broj->spPack);

broj->vpPack.addr = broj->sp.VP;

switch(number->sp.Type) //Dužina podataka vp varijable se automatski bira prema tipu varijable podataka dizajniranom u DGUS sučelju.

{

slučaj 0:

slučaj 5:

broj->vpPack.datLen = 2;

break;

slučaj 1:

slučaj 2:

slučaj 3:

slučaj 6:

broj->vpPack.datLen = 4;

slučaj 4:

broj->vpPack.datLen = 8;

break;

}

broj->vpPack.pBuf = vrijednost;

}

Nakon inicijalizacije, Hsample.sp je pokazivač opisa varijable podataka uzorkovanja napona;Hsample.spPack je komunikacioni pokazivač između OS jezgra i varijable podataka uzorkovanja napona korisničkog interfejsa kroz funkciju DGUS interfejsa;Hsample.vpPack je atribut promjene varijable podataka uzorkovanja napona, kao što je font Boje itd. se također prosljeđuju jezgru korisničkog sučelja preko funkcije DGUS interfejsa.Hsample.vpPack.addr je adresa varijable podataka uzorkovanja napona, koja je automatski dobivena iz funkcije inicijalizacije.Kada promijenite promjenjivu adresu ili varijabilni tip podataka u DGUS sučelju, nema potrebe da ažurirate adresu varijable u OS jezgri sinhrono.Nakon što OS jezgro izračuna varijablu voltage_sample, potrebno je samo izvršiti funkciju Write_Dgus(&Hsample.vpPack) da bi je ažurirala.Nema potrebe za pakiranjem voltage_sample za DGUS prijenos.

Vrijeme objave: Jun-15-2022